![リソグラフィ工程の基礎から先端技術まで解説 [半導体製造工程 2-4]](https://markethink.co.jp/wp-content/uploads/2023/12/semiconductor-equipment-2-4-Litho-banner2.jpg)

リソグラフィ工程は、半導体製造工程において、ウェハ上に回路パターンを形成するための非常に重要な工程です。

本記事では、リソグラフィ工程に関して、「リソグラフィ工程の内容」、「リソグラフィ工程の重要性」、「リソグラフィ工程の歴史」、「最先端のリソグラフィ技術」などリソグラフィ工程の全てを詳しく解説していきます。

関連記事紹介

1.リソグラフィ工程とは

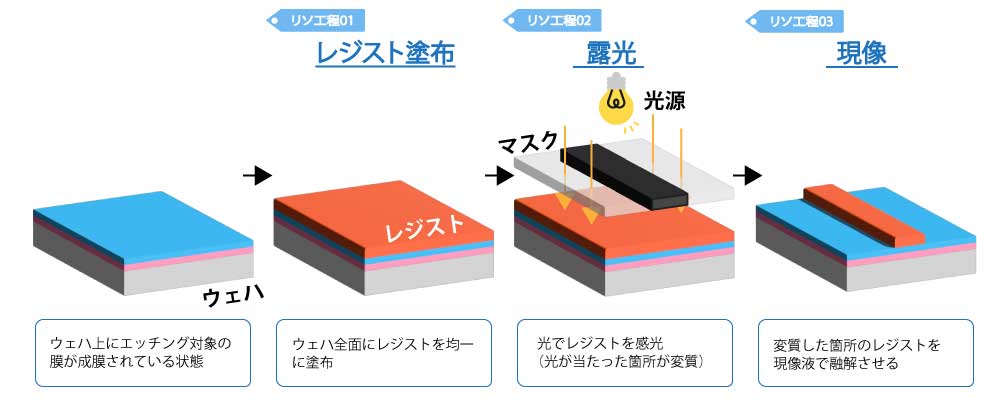

リソグラフィ工程では、”レジスト”という光に反応する材料を用いて、写真と同様の要領で、シリコン上に微細なパターンを形成します。

リソグラフィ工程を大きく分けると

- レジスト塗布:ウェハ全面にレジストを塗布し露光できる状態にする工程

- 露光:光でレジストを感光させる工程

- 現像:光で反応した部分のレジストを現像する工程

の3つの工程からなります。

このリソグラフィ工程の3つの工程を、少し詳しく解説していきます。

リソグラフィ工程 1レジスト塗布

レジスト塗布工程では、特定の波長の光に反応して、性質が変化するレジストをウェハ表面に均一に塗ります。

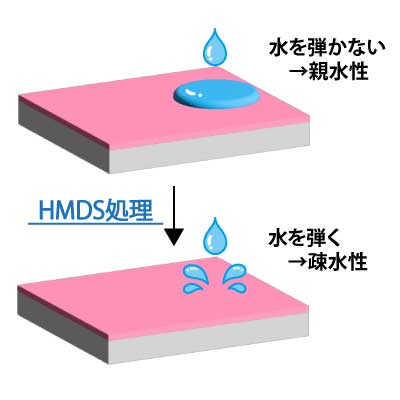

・前処理

まずは、ウェハー表面を疎水性(水を弾く状態)にするためのHMDS処理を行います。

ウェハの表面に酸化膜などを成膜されている場合ウェハ表面が親水性なので、レジスト現像液を使用した際に、現像液がレジストとウェハの間に入りこみ、パターンが剥がれてしまうことがあるためです。

・スピンコート

レジストを高速かつ一様に塗る方法として使用されるのがスピンコートです。

スピンコートは、ウェハの中心に少しのレジスト液をたらし、ウェハを高速で回転させることで、レジスト液が遠心力で全身に広がります。

この時のスピンの速度、時間、レジストの粘度でレジストの膜厚を調整することができます。

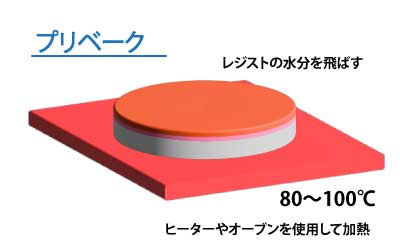

・プリベーク

スピンコート後に、プリベイクによって余分な水分を蒸発させ焼き固めます。

これで露光前の準備が完了します。

レジスト選びは、解像度、露光速度、エッチング耐性などに影響するので非常に重要です。

- 解像度 :反応する光の波長、コントラスト

- 露光速度 :必要な光量

- エッチング耐性:膜厚に影響する粘度、エッチングガスに対する耐性

エッチング耐性を高めるためにレジストを厚くすると、解像度や露光速度が低下するなどトレードオフの関係になるため、よりよいレジストの開発はリソグラフィ工程の発展において必要不可欠です。

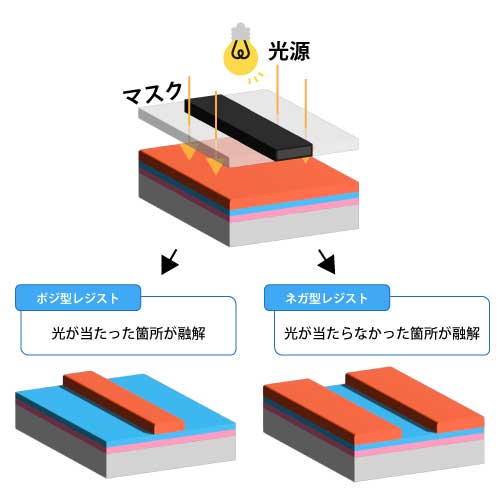

レジストのポジ型とネガ型とはレジストにはポジ型レジストとネガ型レジストが存在します。

- ポジ型レジスト

- ネガ型レジスト

「光が当たった部分が現像時に溶解する」ように変化するレジストです。

そのため、マスクのパターンとウェハ上のパターンが一致します。

「光が当たった部分が現像時に溶解しない」ように硬化する特性をもったレジストです。 そのため、マスクのパターンと反転したパターンが形成されます。

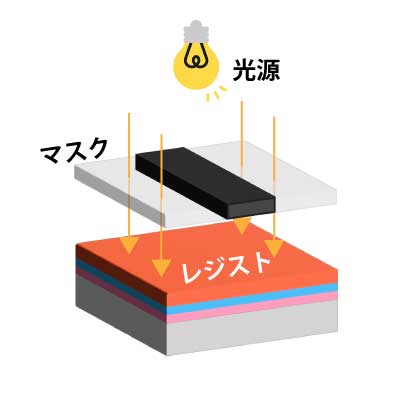

リソグラフィ工程 2露光

露光工程は、マスク越しにレジストに光を当ててレジストを感光させる工程です。

従来は、フォトマスクとウェハを極めて近づけて等倍で露光するプロキシミティ露光が使用されていましたが、微細化が進むにつれ、フォトマスクとウェハの間にレンズを挿入しマスクの1/4のパターンで露光する縮小投影露光が使われるようになりました。

→露光技術の進化に関する詳細は、「3.リソグラフィの進化の歴史」で紹介

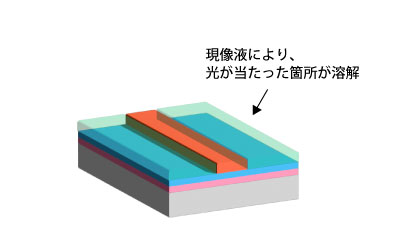

リソグラフィ工程 3現像

現像工程は、現像液とレジストの光が当たった部分(または当たらなかった部分)を反応させ、レジストでパターンを形成する工程です。

・現像

現像液によって、ポジ型の場合には光の当たった部分のレジストをネガ型の場合には光の当たらなかった部分のレジストを融解させます。

・リンス

現像液とレジストの反応を止めるため、リンスでウェハを洗浄します。

・ポストベーク

パターンとして残ったレジストを焼き固め、下地との密着性を高めるため、ウェハを高温で熱します。

ここまでがリソグラフィ工程の一連の工程になります。

2.リソグラフィ工程の重要性

半導体製造工程における、リソグラフィ工程の重要性に関して、3つの視点で紹介していきたいと思います。リソグラフィ工程の登場回数

MOSFETの構造や配線構造を作るためには、イオン注入する箇所やエッチングする箇所を限定する必要があるため、それらの工程の前には必ずリソグラフィ工程が必要になります。

そのため、「成膜」→「リソグラフィ」→「エッチング」→「リソグラフィ」→「イオン注入」→「リソグラフィ」→・・・・という形で、リソグラフィ工程は半導体製造工程の中で何度も繰り返されます。

これを理由に、半導体工場をレイアウトする際にリソグラフィ工程が半導体工場の中心に配置されることからも、その重要性は明白です。

リソグラフィ工程のコスト割合

リソグラフィ工程のコストは非常に高く半導体製造工程全体に対して30%〜40%にもなります。

これは、リソグラフィ工程が繰り返し行われるということに加えて、ArFの露光装置で約20億円、EUVの露光装置においては200億円と装置が高価ということもあります。

よって、リソグラフィのコスト削減が、半導体製造工程全体のコスト削減におおきな影響を及ぼすという非常に重要な工程であることがわかります。

リソグラフィ工程と微細化

デバイスの高性能、低消費電力、小型化を実現するための微細化に向けて、半導体製造工程は日々研究開発が進んでいます。

リソグラフィ工程で露光できる最小線幅以上に微細な加工をすることは困難なので、この半導体製造工程の微細化の歴史は、リソグラフィ工程発展の歴史といっても過言ではありません。

微細化におけるリフォグラフィ工程にかける努力から、その重要性がみえてきます。

ということで、次に微細化と共に歩んできたリソグラフィ工程の歴史を紹介したいと思います。

3.リソグラフィの進化の歴史

半導体製造工程の微細化と露光装置の関係は密接に関係しています。

ここからは、微細化のテクノロジーノードとリソグラフィ工程(主に露光機)の関係を紹介します。

1µmノード以前のリソグラフィ

1970年代g線(436nm)コンタクト露光・プロキシミティ露光1µmノード以前の露光装置はg線(436nm)を用いた、コンタクト露光やプロキシミティ露光などの装置が用いられました。

コンタクト露光やプロキシミティ露光は、マスクのパターンとウェハのパターンのサイズが同じ、等倍の露光です。

コンタクト露光は、文字通り、ウェハとマスクを物理的に接触(コンタクト)させて露光する方法です。

光が回り込まない分、解像力が得られますが、接触によりマスクにレジストのゴミがつくなどするため、マスクの寿命や歩留りに課題がありました。

プロキシミティ露光は、ウェハとマスクの間にわずかな隙間を残して露光する方法です。

光が回り込むため、解像力が落ちますが、コンタクト露光のようにマスクにレジストのゴミがつくなどは避けられることがメリットでした。

1µmノードのリソグラフィ

1980年代i線(365nm)ステッパー1µmノードになるとより波長の短いi線(365nm)が使われるようになり、さらにマスクとウェハの間にレンズを挿入し、パターンを縮小して投影する「縮小投影露光」が用いられるようになりました。

この、縮小投影露光をステップアンドリピートで繰りかえしながらウェハ全面を露光するため、露光装置はステッパーと呼ばれます。

250-130nmノードのリソグラフィ

1990年代KrFエキシマレーザー(248nm)ステッパー・スキャナー250nmノード以下になると、さらに波長の短いKrFエキシマレーザー(248nm)が導入されました。

この世代では、ステップアンドリピートで露光する「ステッパー」だけではなく、スキャンにより露光する「スキャナー」も登場しました。

以下に、ステッパーとスキャナーをスループット(速度)、解像度、コストなどの比較を紹介します。

| ステッパー | スキャナー | |

|---|---|---|

| 機構 | ステップアンドリピートで露光する(マスクとウェハーが静止した状態で露光) | マスクとウェハーが同期して移動しながら露光する |

| 縮小露光比率 | 5:1 | 4:1 |

| スループット(速度) | △ | ○ |

| 解像度 | ○ | △ |

| コスト | ○ | △ |

130-90nmノードのリソグラフィ

2000年代ArFエキシマレーザー(193nm)ステッパー・スキャナー130nmノード以下になると、ArFエキシマレーザー(193nm)が使用されるようになります。

このノードまでは、基本的には光源の波長を短くすることで微細化が実現されてきました。

ステッパーやスキャナなどの露光機の構成は基本的にはKrFと同じですが、光源の波長が短くなった分、原理的に22%程度の微細加工が可能になりました。

65-45nmノードのリソグラフィ

2000年代ArFエキシマレーザー(193nm)液浸ステッパーArFエキシマレーザー(193nm)での微細化は、90nmノードで限界を迎え、より短い波長はF2レーザー(157nm)やEUV(13.5nm)となりますが、この頃F2レーザーやEUVは様々な課題があり、実用レベルにはない状況でした。

そこで、65nmノード以降は、ArFエキシマレーザーと他の技術を組み合わせることで微細化を実現していきます。

この世代で使用されるようになったのが、液浸露光です。

液浸露光は、レンズとウェハの間を”空気”よりも屈折率の高い”水”で満たすことで、より高い解像度を達成することができる露光方法です。

F2レーザー等の課題に比べ、レンズとウェハの間に純水をたらすという方が課題が少なく、コスト的にも安価という点で画期的な手法でした。

また、この頃から、現像後のパターンが理想的な形状になるようにマスクパターンに補正をかけるOPC処理が積極的にされるようになりました。

液浸露光やOPCの複合的な技術の進化により、苦労の末なんとかArFエキシマレーザーでこのノードを実現した形です。

32-10nmノードのリソグラフィ

2010年代ArFエキシマレーザー(193nm)液浸ステッパー(マルチパターニング)32nmノード以降になると、マルチパターニング技術が導入されるようになりました。

マルチパターニングは、2回または3回露光することで、1つのパターンを形成する手法です。

2回露光のダブルパターニングにおいても、種類が「LELE」、「SADP」、「SAQP」と3種類あります。

マルチパターニングは、露光時の位置合わせのズレが、出来上がりパターンのスペースに影響するため、露光装置には高い精度での位置合わせが求められました。

→マルチパターニングの種類を解説(準備中)

7-3nmノードのリソグラフィ

2020年代EUV(13.5nm)EUV露光装置この世代で、ついに、EUV(13.5nm)の露光装置が実用化されました。

EUVには、「EUV光源の出力が出ない」、「EUV光は真空である必要がある」、「ガラスで集光できないのでマスクを含め反射光学系になる」、「透過率の高いペリクル(マスクを保護する材料)がない」などなど、様々な問題がありましたが、それらが研修開発により解決されています。

そして、2021年末までに世界中で100台以上のEUV露光装置が稼働しています

今後も、更なる微細化が期待されており、High-NAのEUVリソグラフィなどの技術が研究開発されています。

4.最先端のリソグラフィ技術

2023年7月現在、最先端の半導体技術ロードマップ"IRDS"で、リソグラフィに求められるであろうハーフピッチは以下のように7-8nmまで微細化が進むというという形で示されています。| 2022 | 2025 | 2028 | 2031 | 2034 | 2037 | |

|---|---|---|---|---|---|---|

| MPU/ASIC Metal ミニマムハーフピッチ (nm) |

12 | 10 | 8 | 8 | 8 | 8 |

| DRAM ミニマムハーフピッチ (nm) |

17 | 14 | 11 | 8 | 8 | 7 |

ここで、すでにテクノロジーノードが3nmなのに、なぜ2022年のハーフピッチが12nmになっているのかと思われた方もいるかと思います。

微細化によって違いが出てきた「テクノロジーノード」と「ハーフピッチ」の違いが気になった方はこちらをご確認ください。

2023年現在は、EUV(13.5nm)のリソグラフィをいかに改善して、要求されるハーフピッチに対応していくかという点に注目が集まっています。

同一波長で解像度を高めるための有効な手段は、開口率(NA)の増大であり、ASMLの高NA-EUVリソグラフィ(Carl Zeiss製の0.55 NA光学系を使用)が、2024年にチップメーカーに導入される計画があります。

今後の、さらなる高NA-EUVリソグラフィの課題をIDRS2022のロードマップから抜粋すると以下になります。

- パターン崩壊による欠陥への耐性

- フォトンショットノイズと生産性要件に対応できる光源の開発

- 高NAと小さな焦点深度の両立

- 高NAと高コントラストを両立するための偏光制御

- リソグラフィシミュレーション

- マスク製造および計測インフラの整備

- 大型ダイ対応のソリューション

- 高NA EUVリソグラフィのコスト低減

中長期的に、これらの課題が克服されることで、NA0.7の高NA-EUVが実現されると考えられます。

同時に、6.Xnmといった、EUVより波長の短い光源への以降も検討されていますが、「光源の実現」、「マスク(多層コーティング)」、「レジスト」など高NA化と比較して非常に多くの課題があります。

5.リソグラフィ工程のまとめ

リソグラフィ工程は、半導体製造工程において、ウェハー上に微細なパターンを転写する工程です。

そして、このプロセスは製品の性能や製造コストに直接的な影響を及ぼすため、半導体製造工程の中でも非常に重要な工程として位置付けられています。

リソグラフィの進化は、1970年代のg線(436nm)を用いた方法から現代のEUV(13.5nm)露光装置へと進み、各世代で新しい技術が導入されました。

この技術進化は、さらなる微細化を目指し、今も開発が続けられています。